Giới thiệu về IC logic và IC latch 74HC595

Trong bài này chúng ta sẽ tìm hiểu về các loại IC Logic thông dụng và IC chốt 74HC595.

I. Các loại IC Logic:

1. Sơ lược về mức logic:

Mức Logic là 1 định nghĩa trong toán học về nhị phân. Có 2 mức là mức “1” (phổ biến là tương ứng với mức điện áp 12*VCC) và mức “0” (tương ứng với điện áp 1⁄2 VCC). Mức “1” cũng còn được gọi là mức HIGH (mức cao). Mức “0” cũng được gọi là mức LOW (mức thấp).

* VCC là điện áp cấp nguồn cho chip (IC) hoạt động, ví dụ 5V, 3.3V, 12V…

2. Phép toán logic và các loại IC logic:

a. NOT:

Phép toán này còn được gọi là phép đảo trạng thái logic. Cụ thể là nếu ngõ vào có mức logic là 1 thì ngõ ra sẽ có mức logic là 0 và ngược lại.

Ký hiệu toán: x’= với x là tín hiệu vào, và x’ là ngõ ra.

Ký hiệu trên mạch điện và bảng giá trị:

IC NOT: 74HC14. Các em xem datasheet để biết rõ về chân cẳng của nó (để biết chân nào là ngõ vào (Input), chân nào là ngõ ra (output), chân cấp nguồn (VCC) và chân nối đất (GND)).

*GND (Ground) thường được gọi là chân “đất”, thực tế không phải là dùng dây điện nối chân đó xuống “đất”

Nguồn cấp cho mạch điện tử hoạt động là nguồn DC (một chiều), trong đó cực dương nối vào chân VCC, và cực âm nối vào chân GND.

b. AND:

Với toán tử này, ngõ ra chỉ bằng 1 chỉ khi tất cả các ngõ vào bằng 1.

Ký hiệu trên mạch và bảng giá trị:

IC 74HC08:

c. NAND:

Toán tử trên ngược lại với AND. Ngõ ra bằng 0 chỉ khi tất cả ngõ vào bằng 1.

Ký hiệu và bảng giá trị:

IC 74HC00:

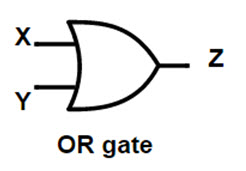

d. OR:

Ngõ ra bằng 1 khi có ít nhất 1 ngõ vào bằng 1. Ngược lại ngõ ra bằng 0 khi tất cả các ngõ vào bằng 0.

Ký hiệu và bảng giá trị:

IC OR: 74HC32:

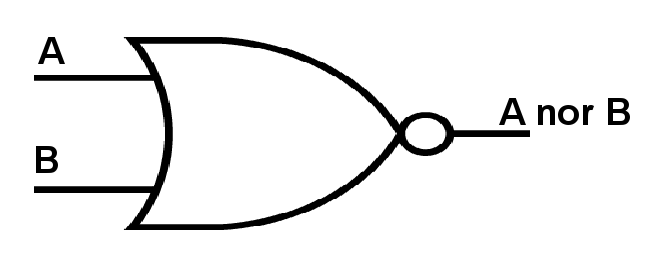

e. NOR:

Ngược lại với toán tử OR, giá trị ngõ ra bằng 0 khi có ít nhất một ngõ vào bằng 1, ngược lại ngõ ra bằng 1 khi tất cả các ngõ vào bằng 0.

Ký hiệu và bảng giá trị:

IC NOR: 74HC02

f. XOR:

Với phép toán này, ngõ ra bằng 1 khi hai ngõ vào khác nhau. Ngược lại, nếu hai ngõ vào giống nhau thì ngõ ra bằng 0.

Ký hiệu và bảng giá trị:

IC XOR: 74HC86

g. XNOR:

Toán tử trên ngược với pháp nor, ngõ ra chỉ bằng 1 khi hai ngõ vào bằng nhau.

IC XNOR: 74HC266

3. IC 74HC595:

IC 74HC595 còn gọi là IC dịch chốt với mối quan hệ “ vào nối tiếp và ra song song 8 bit” và có 3 trạng thái ngõ ra.

“ Dịch “ ở đây có thể hiểu một cách đơn giản ta có thể đưa lần lượt nhiều giá trị logic vào một ngõ vào của IC đó để nó lưu vào bộ nhớ chờ đến khi có lệnh xử lí.

Đối với ngõ vào nối tiếp: các giá trị được nạp vào IC một cách từ từ ở từng thời điểm khác nhau trên cùng một ngõ vào.

Đối với ngõ ra song song: có nhiều ngõ ra và các giá trị sẽ được nạp vào IC trước đó được xuất cùng một lúc.

Sơ đồ chân IC 74HC595:

- Các chân từ 1 tới 7 và chân số 15: là ngõ ra của IC (ứng với Q 0 và Q 1 ,…,Q 7).

- Chân DS (chân số 14): là ngõ vào của IC (đây là IC vào nối tiếp nên ta chỉ cần 1 ngõ vào là đủ).

- Chân 16 – VCC: là chân cấp nguồn dương (từ 2V đến 6V).

- Chân số 8 GND: là chân cấp Ground – cực (-) của nguồn.

- Chân SHCP: là chân đưa xung clock (xung nhịp) vào IC và khi có cạnh lên của xung thì IC đưa tín hiệu ở ngõ vào vào bộ nhớ của IC để chờ xử lý.Vậy cạnh lên của xung là như thế nào ?

Cạnh lên là khi xung clock chuyển trạng thái từ 0 lên 1, còn cạnh xuống là thời điểm khi chuyển từ 1 xuống 0. - Chân STCP: là chân đưa xung clock vào IC để khi có cạnh lên của xung thì IC đưa toàn bộ 8 bit data đã được lưu (đã nói ở chân SHCP) ra ngõ ra của IC.

- Chân MR : là chân reset IC (tức là trả IC về trạng thái ban đầu). Khi chân này tích cực thì toàn bộ bộ nhớ của IC sẽ bị xoá tất cả bằng 0, tuy nhiên lưu ý là lúc này tín hiệu ở ngõ ra không bị xoá mà vẫn giữ nguyên giá trị trước đó) và chân này tích cực mức thấp (LOW active) có nghĩa là muốn reset IC thì phải đưa 0V vào chân này.

- Chân OE: là chân Output Enable chân khi được tích cực thì mới cho phép ta điều chỉnh được giá trị ngõ ra.

- Chân Q7S: Chữ S ở đây là viết tắt cho từ Serial (nối tiếp) chân này thường được dùng khi ta nối tiếp các IC 74HC595 với nhau . Khi bit thứ 9 được đưa vào thanh ghi dịch thì bit cuối cùng tại Q7 hiện tại sẽ được dịch sang chân Q7S. Và cứ như thế bit thứ 10 , 11 , … thì bit trên con IC nối tiếp cũng dẽ được dịch theo chiều như chiều trên từ Q0 –> Q7.

Mạch mở rộng ngõ ra:

4. Mạch tạo password:

File mô phỏng Proteus password circuit:link file proteus

Sơ đồ mạch:

Chức năng của mạch này là tạo được các tín hiệu ngõ ra của con 74HC595 bằng 3 nút nhấn.

Nguyên lý hoạt động của mạch:

+ Khi ta nhấn Button Set 1 thì sẽ đưa mức logic 1 vào chân SDI ( Serial Data Input) đồng thời qua diode D1 xuống nạp điện cho tụ C2 sao 1 thời gian thì mức điện áp đăt trên chân SRCLK là 5v ( logic 1) như vậy tụ C2 là để tạo thời gian delay giữa tín hiệu vào và cạnh xung của xung clock đảm bảo cho IC nhận đúng tín hiệu vào để đưa vào bộ nhớ đệm chờ khi có mức logic 1 đặt vào chân RCLK thì thực hiện đưa data ra ngõ ra.

+ Còn khi ta nhấn Button Set 0 thì chỉ có chức năng nạp điện cho tụ C2 chứ không thể đưa tín hiệu vào chân SDI được do sự phân cực ngược của diode. Do đó mức logic đưa vào chân SDI trong trường hợp này là 0 (0v do có điện trở kéo xuống mass). IC sẽ nhận được data là 0.

+ Khi nhấn SW 3 thì ta sẽ đưa mức logic vào chân RCLK thực hiện đưa data lưu trong bộ nhớ đệm của IC ra các ngõ ra.

+ Còn khối mạch reset bình thường khi không có tác động gì thì mức logic đưa vào chân CLR là 1 ( chân này tích cực thấp). Khi có sự kiện nhấn nút SW5 thì chân CLR sẽ được đưa xuống mass ( logic 0) -> IC sẽ bị reset, toàn bộ ngõ ra sẽ về 0.