Tài liệu này trình bày về các nguyên tắc hoạt động của dòng cách ly số ISO72xx của hãng TI với kĩ thuật cách ly mới hoạt động tốt trong dải băng thông rộng từ DC cho tới 150Mbps. Là một giải pháp cách ly hữu hiệu trong nhu cầu truyền dữ liệu tốc độ cao.

Tài liệu này cũng hướng dẫn cách thiết kế PCB với nhiễu EMI thấp (nhiễu điện từ), là những thông tin quan trọng khi thiết kế các PCB chạy ở tần số cao.

Được dịch từ tài liệu slla284 - Digital Isolator Design Guide, Texas Instruments.

I. Đôi nét về dòng Isolator của TI :

Các dòng Digital IsolatorTexas Instruments có tính năng cách ly tín hiệu số, truyền dữ liệu theo 1 hoặc 2 chiều, tốc độ truyền dữ liệu nhanh (lên tới 150 Mbps), giảm nhiễu EMI, và tuổi thọdài hơn so với các linh kiện cách ly khác. Digital Isolator sử dụng kĩ thuật cách ly bằng điện dung, nhờ đó cải thiện hiệu suất củahệ thống và giảm chi phí chống nhiễu.

Công nghệ điện dung của TI cho phép chống nhiễu các thiết bịcảm ứng, chống nhiễu từ các từ trường ngoài(thường xuyên xảy ra trongmôi trường công nghiệp,có thể gây ra sai lệch tín hiệu).

Các linh kiện ISO (Digital Isolator) của T Icó thể cách ly tới 4000V và tuổi thọ>25năm(so với 7-10 năm của các loại linh kiện cách ly khác). Đây là những yêu cầu quan trọng trong các ứng dụng công nghiệp nơi mà điện áp thường thay đổi đột ngột, có thể làm suy giảm hiệu suất và tuổi thọ thiết bị.

ISO được cấp 2 nguồn độc lập, chặn điện áp cao, và ngăn chặn dòng nhiễu từ từ các phần lân cận gây cản trở hoặc hư hại tới các mạch cảm biến.

II. Những điều cần biết khi thiết kế mạch hoạt động ở tần số cao (hoặc trong mạch có các đường dây tín hiệu – đường dây truyền nhận dữ liệu chạy ở tần số cao)

Mạch hoạt động ở tần số cao, nếu PCB thiết kế không tốt sẽ gây ra nhiễu, khiến dữ liệu truyền đi trên board bị suy hao hoặc sai lệch, nhiều khi mạch hoạt động không ổn định, thậm chí là chạy sai hoàn toàn.

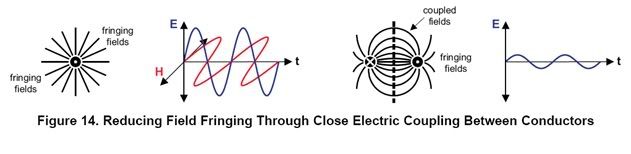

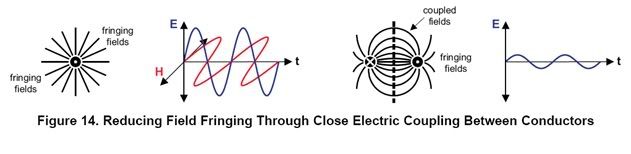

VD: Xem xét một dây dẫn đơn mang dòng AC, Hình 14, electric coupling yếu hoặc không có electric coupling sẽ cho phép sóng điện từ ngang (TEM wave - transversal electromagnetic wave) sinh ra bởi dòng điện, tản môi trường bên ngoài, gây ra nhiễu trường điện từ EMI nghiêm trọng.

Giả sử có một dây dẫn thứ 2, ở gần dây cũ, mang một dòng điện y chang dây 1 nhưng ngược chiều. Trong trường hợp này, từ trường của 2 dây bị triệt tiêu, và điện trường được liên kết chặt chẽ (tightly couple).TEM waves của 2 dây bị triệt tiêu, không tản ra môi trường ngoài. Phần trường tản nhỏ chỉ có thể liên kết với nhau ở xa. Vì vậy, nhiễu EMI nhỏ đi rất nhiều.

Do đó, đối với các mạch tần số cao, hoặc ít nhất là trên mạch có các đường dây truyền tín hiệu với tần số cao, thì việc thiết kế layout và đi dây cho nó trở nên quan trọng vô cùng.

Đối với mạch chạy tần số thấp, khi thiết kế PCB, vẫn nên tuân theo các hướng dẫn trong tài liệu sau (giảm thiểu nhiễu EMI, đảm bảo mạch hoạt động ổn định).

1. Nhiễu EMI là gì?

Nhiễu điện từ (EMI, còn được gọi là nhiễu tần số vô tuyến điện hoặc RFI) là một rối loạn có ảnh hưởng đến một mạch điện do cảm ứng điện hoặc bức xạ điện từ phát ra từ một nguồn bên ngoài. Các nhiễu này có thể gây cản trở, ngắt quãng, hoặc làm suy hao tín hiệu. Nguồn nhiễu có thể là bất kỳ đối tượng nào, nhân tạo hoặc tự nhiên.

2. Với những board mạch digital hoạt động ở tần số từ 150Mbps trở xuống (hay là thời gian lên –rise time và xuống –fall time của tín hiệu lớn hơn 1ns), và các đường mạch có độ dài tới 10 inches thì có thể dùng board FR-4 (thuỷ tinh – epoxy) để làm PCB.

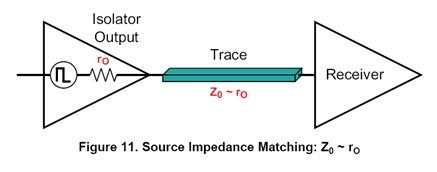

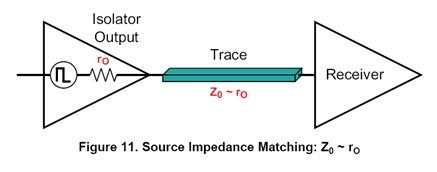

3. Ðường dây truyền tải có trở kháng điều khiển được:

- Là đường dây có trở kháng Z0 có thể được điều khiển dựa vào thay đổi vào cấu trúc hình học của đường mạch (trace)

- Thường được dùng để phối hợp các trở kháng ở các mối nối trung gian trong đường dây truyền tải, ví dụ nhu giữa cáp và đầu jack, để giảm thiểu tổn hao tín hiệu.

- Đối với Digital Isolators, các đường mạch được điều khiển trở kháng sao cho gần bằng trở kháng ra (Z0~r0) – theo định lí phối hợp trở kháng nguồn.

4. Tầm quan trọng của việc phủ mass (phủ GND)

Khi layout 2 lớp, mặt BOTTOM nên đi ít dây hơn, và phần lớn diện tích ở mặt BOTTOM nên được phủ mass. Vì phần mass sẽ đóng vai trò như một đường phản hồi(return path) triệt tiêu các tín hiệu gây nhiễu.

(Thật ra, để thực hiện các PCB chạy ở tần số cao, giảm nhiễu, ta cần PCB ít nhất có 4 lớp, tuy nhiên hiện nay việc làm mạch với số lượng nhỏ ở ta chỉ mới thuận lợi đối với các PCB 2 lớp )

)

5. Ý nghĩa của các loại tụ trong việc giảm nhiễu EMI:

- Tụ bulk: tụ điện dung lớn, gọi là bulk capacitors, (vd 10 uF), gần nguồn cung cấp, chẳng hạn tại chip ổn áp nguồn (voltage regulator), hay tại nơi cấp nguồn vào PCB : để ổn áp cho nguồn.

- Tụ Decoupling: như là một nguồn sạc tại chỗ (local source of charge) cung cấp cho các ICs cần một dòng điện đáng kể để đáp ứng hoạt động chuyển mạch nội. Thiếu tụ decoupling có thể gây ra thiếu dòng cung cấp cho IC để nó hoạt động bình thường, hậu quả là tín hiệu không được bảo toàn (bị suy hao), xảy ra lỗi dữ liệu.

- Tụ by-pass: tụ có điện dung nhỏ hơn, gọi là bypass capacitors (0.1-uF hoặc 0.01-uF) tại các linh kiện.

6. Nên đi dây với góc 45 hay 135 độ mà không đi dây bẻ vuông góc

Vì góc 90o tăng bề rộng thực sự của đường → tăng trở kháng → sai lệch trở kháng, dẫn tới bị phản xạ nhiều hơn.

7. Không nên đi đường tín hiệu trên nhiều lớp (layer)

Khi đi các đường tín hiệu, cần tránh thay đổi layer (tránh đi các traces tín hiệu trên nhiều layer khác nhau) vì nó sẽ dẫn tới tăng hệ số hỗ cảm của đường tín hiệu=> tăng nhiễu EMI

Nếu không thể tránh khỏi việc đi dây tín hiệu xuyên qua nhiều lớp, phải liên kết mỗi via của đường tín hiệu với một via của đường return-trace. Trong trường hợp này, sử dụng kích thước via nhỏ nhất có thể để sự tăng hệ số hỗ cảm là ít nhất.

Kết luận: Trên đây chỉ là 1 số nội dung tóm tắt, chưa đầy đủ (vì nhiều hình quá, mình không post hết được

(vì nhiều hình quá, mình không post hết được  , he he), mời các bạn download tài liệu đầy đủ ở đây :p <- Click vào đây .

, he he), mời các bạn download tài liệu đầy đủ ở đây :p <- Click vào đây .

Tài liệu này cũng hướng dẫn cách thiết kế PCB với nhiễu EMI thấp (nhiễu điện từ), là những thông tin quan trọng khi thiết kế các PCB chạy ở tần số cao.

Được dịch từ tài liệu slla284 - Digital Isolator Design Guide, Texas Instruments.

I. Đôi nét về dòng Isolator của TI :

Các dòng Digital IsolatorTexas Instruments có tính năng cách ly tín hiệu số, truyền dữ liệu theo 1 hoặc 2 chiều, tốc độ truyền dữ liệu nhanh (lên tới 150 Mbps), giảm nhiễu EMI, và tuổi thọdài hơn so với các linh kiện cách ly khác. Digital Isolator sử dụng kĩ thuật cách ly bằng điện dung, nhờ đó cải thiện hiệu suất củahệ thống và giảm chi phí chống nhiễu.

Công nghệ điện dung của TI cho phép chống nhiễu các thiết bịcảm ứng, chống nhiễu từ các từ trường ngoài(thường xuyên xảy ra trongmôi trường công nghiệp,có thể gây ra sai lệch tín hiệu).

Các linh kiện ISO (Digital Isolator) của T Icó thể cách ly tới 4000V và tuổi thọ>25năm(so với 7-10 năm của các loại linh kiện cách ly khác). Đây là những yêu cầu quan trọng trong các ứng dụng công nghiệp nơi mà điện áp thường thay đổi đột ngột, có thể làm suy giảm hiệu suất và tuổi thọ thiết bị.

ISO được cấp 2 nguồn độc lập, chặn điện áp cao, và ngăn chặn dòng nhiễu từ từ các phần lân cận gây cản trở hoặc hư hại tới các mạch cảm biến.

II. Những điều cần biết khi thiết kế mạch hoạt động ở tần số cao (hoặc trong mạch có các đường dây tín hiệu – đường dây truyền nhận dữ liệu chạy ở tần số cao)

Mạch hoạt động ở tần số cao, nếu PCB thiết kế không tốt sẽ gây ra nhiễu, khiến dữ liệu truyền đi trên board bị suy hao hoặc sai lệch, nhiều khi mạch hoạt động không ổn định, thậm chí là chạy sai hoàn toàn.

VD: Xem xét một dây dẫn đơn mang dòng AC, Hình 14, electric coupling yếu hoặc không có electric coupling sẽ cho phép sóng điện từ ngang (TEM wave - transversal electromagnetic wave) sinh ra bởi dòng điện, tản môi trường bên ngoài, gây ra nhiễu trường điện từ EMI nghiêm trọng.

Giả sử có một dây dẫn thứ 2, ở gần dây cũ, mang một dòng điện y chang dây 1 nhưng ngược chiều. Trong trường hợp này, từ trường của 2 dây bị triệt tiêu, và điện trường được liên kết chặt chẽ (tightly couple).TEM waves của 2 dây bị triệt tiêu, không tản ra môi trường ngoài. Phần trường tản nhỏ chỉ có thể liên kết với nhau ở xa. Vì vậy, nhiễu EMI nhỏ đi rất nhiều.

Do đó, đối với các mạch tần số cao, hoặc ít nhất là trên mạch có các đường dây truyền tín hiệu với tần số cao, thì việc thiết kế layout và đi dây cho nó trở nên quan trọng vô cùng.

Đối với mạch chạy tần số thấp, khi thiết kế PCB, vẫn nên tuân theo các hướng dẫn trong tài liệu sau (giảm thiểu nhiễu EMI, đảm bảo mạch hoạt động ổn định).

1. Nhiễu EMI là gì?

Nhiễu điện từ (EMI, còn được gọi là nhiễu tần số vô tuyến điện hoặc RFI) là một rối loạn có ảnh hưởng đến một mạch điện do cảm ứng điện hoặc bức xạ điện từ phát ra từ một nguồn bên ngoài. Các nhiễu này có thể gây cản trở, ngắt quãng, hoặc làm suy hao tín hiệu. Nguồn nhiễu có thể là bất kỳ đối tượng nào, nhân tạo hoặc tự nhiên.

2. Với những board mạch digital hoạt động ở tần số từ 150Mbps trở xuống (hay là thời gian lên –rise time và xuống –fall time của tín hiệu lớn hơn 1ns), và các đường mạch có độ dài tới 10 inches thì có thể dùng board FR-4 (thuỷ tinh – epoxy) để làm PCB.

3. Ðường dây truyền tải có trở kháng điều khiển được:

- Là đường dây có trở kháng Z0 có thể được điều khiển dựa vào thay đổi vào cấu trúc hình học của đường mạch (trace)

- Thường được dùng để phối hợp các trở kháng ở các mối nối trung gian trong đường dây truyền tải, ví dụ nhu giữa cáp và đầu jack, để giảm thiểu tổn hao tín hiệu.

- Đối với Digital Isolators, các đường mạch được điều khiển trở kháng sao cho gần bằng trở kháng ra (Z0~r0) – theo định lí phối hợp trở kháng nguồn.

4. Tầm quan trọng của việc phủ mass (phủ GND)

Khi layout 2 lớp, mặt BOTTOM nên đi ít dây hơn, và phần lớn diện tích ở mặt BOTTOM nên được phủ mass. Vì phần mass sẽ đóng vai trò như một đường phản hồi(return path) triệt tiêu các tín hiệu gây nhiễu.

(Thật ra, để thực hiện các PCB chạy ở tần số cao, giảm nhiễu, ta cần PCB ít nhất có 4 lớp, tuy nhiên hiện nay việc làm mạch với số lượng nhỏ ở ta chỉ mới thuận lợi đối với các PCB 2 lớp

)

)5. Ý nghĩa của các loại tụ trong việc giảm nhiễu EMI:

- Tụ bulk: tụ điện dung lớn, gọi là bulk capacitors, (vd 10 uF), gần nguồn cung cấp, chẳng hạn tại chip ổn áp nguồn (voltage regulator), hay tại nơi cấp nguồn vào PCB : để ổn áp cho nguồn.

- Tụ Decoupling: như là một nguồn sạc tại chỗ (local source of charge) cung cấp cho các ICs cần một dòng điện đáng kể để đáp ứng hoạt động chuyển mạch nội. Thiếu tụ decoupling có thể gây ra thiếu dòng cung cấp cho IC để nó hoạt động bình thường, hậu quả là tín hiệu không được bảo toàn (bị suy hao), xảy ra lỗi dữ liệu.

- Tụ by-pass: tụ có điện dung nhỏ hơn, gọi là bypass capacitors (0.1-uF hoặc 0.01-uF) tại các linh kiện.

6. Nên đi dây với góc 45 hay 135 độ mà không đi dây bẻ vuông góc

Vì góc 90o tăng bề rộng thực sự của đường → tăng trở kháng → sai lệch trở kháng, dẫn tới bị phản xạ nhiều hơn.

7. Không nên đi đường tín hiệu trên nhiều lớp (layer)

Khi đi các đường tín hiệu, cần tránh thay đổi layer (tránh đi các traces tín hiệu trên nhiều layer khác nhau) vì nó sẽ dẫn tới tăng hệ số hỗ cảm của đường tín hiệu=> tăng nhiễu EMI

Nếu không thể tránh khỏi việc đi dây tín hiệu xuyên qua nhiều lớp, phải liên kết mỗi via của đường tín hiệu với một via của đường return-trace. Trong trường hợp này, sử dụng kích thước via nhỏ nhất có thể để sự tăng hệ số hỗ cảm là ít nhất.

Kết luận: Trên đây chỉ là 1 số nội dung tóm tắt, chưa đầy đủ

(vì nhiều hình quá, mình không post hết được

(vì nhiều hình quá, mình không post hết được  , he he), mời các bạn download tài liệu đầy đủ ở đây :p <- Click vào đây .

, he he), mời các bạn download tài liệu đầy đủ ở đây :p <- Click vào đây .